мікроконтролер AVR ATmega128 виробництва компанії Atmel має обсяг вбудованої cтатіческой оперативної пам'яті з довільним доступом 4 КБ. Однак, при розробці деяких типів додатків, навіть цього обсягу може бути недостатньо. Наприклад, якщо програма має справу з великими обсягами даних або управляє операційною системою реального часу, то даний обсяг SRAM дуже швидко вичерпається.

Для вирішення цієї проблеми можна використовувати вбудований в мікроконтролер ATmega128 інтерфейс зовнішньої пам'яті, який дозволяє розширити обсяг пам'яті SRAM до 64 КБ.

Для експериментів можна використовувати будь-яку отладочную плату на базі мікроконтролера ATmega128, бажано з встановленим коннектором XRAM інтерфейсу. Крім того, буде потрібно наявність на платі драйвера і порту RS-232 для спостереження налагоджувальної інформації в термінальній програмі на ПК, напрмер для цього можна застосувати мікросхему MAX232 з соотвтетствующімі зовнішніми компонентами.

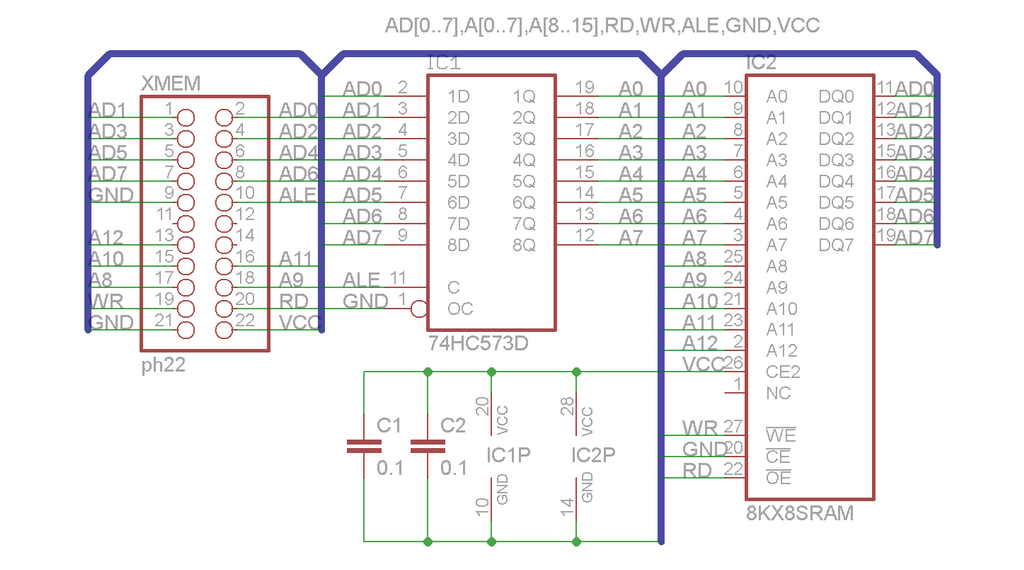

Для підключення додаткової зовнішньої пам'яті необхідно виготовити модуль розширення, який буде підключатися до отладочной платі. Модуль містить встановлену мікросхему SRAM AS6C6264 , Виробництва компанії Alliance Memory, мікросхему для управління пам'яттю 74HC573 (Восьмизарядний регістр-клямка) і коннектор інтерфейсу XRAM.

Підключення зовнішнього статичного ОЗП до AVR-мікроконтролера

Характеристики інтерфейсу зовнішньої пам'яті позволяюют використовувати його не тільки для підключення до зовнішнього статичного ОЗП або флеш-пам'яті, але і в якості інтерфейсу з зовнішніми периферійними пристроями, наприклад, ЖК-дисплеями, АЦП і ЦАП. Його основними відмітними особливостями є:

- Можливість завдання чотирьох різних за тривалістю станів очікування, в т.ч. без стану очікування.

- Можливість установки різних станів очікування для різних секторів зовнішньої пам'яті (розмір сектора конфігурується).

- Можливість вибору кількості задіяних розрядів в старшому адресному байті.

- Пристрій запам'ятовування стану шини для мінімізації споживання струму (опціонально).

Інтерфейс XRAM характеризується високою швидкодією через що фіксація адреси повинна виконуватися з обережністю при частотах понад 8 МГц при 4 В і 4 МГц при 2.7 В.

При використанні більш високих частот застосування регістрів застарілої серії 74HC буде неадекватним. Інтерфейс зовнішньої пам'яті розроблений для сумісності з регістрами серії 74AHC. Однак, більшість регістрів може бути використано, якщо вони відповідають вимогам тимчасової діаграми. До основних параметрів, що характеризують фіксацію адреси, відносяться:

- Тривалість затримки на поширення сигналу з входу D на вихід Q.

- Час установки даних перед тим як G стане рівним 0.

- Час утримання даних (адреси) після установки низького рівня на вході G.

Інтерфейс XRAM мікроконтролера складається з:

- AD [0..7] (висновки порту А) - мультиплексованих молодша шина адреси / шина даних.

- A [8..15] (висновки порту C) - Cтарший шина адреси (з конфігурованим числом розрядів).

- ALE (Висновок PG2) - cтроб адреси зовнішньої пам'яті.

- RD (висновок PG1) - інвертований стрибає читання із зовнішньої пам'яті.

- WR (висновок PG0) - інвертований стрибає записи в зовнішню пам'ять.

Принципова схема модуля розширення пам'яті

Натисніть для збільшення

AS6C6264 -мікросхема КМОП статичної оперативної пам'яті з довільним доступом 65536 біт (8192 слова по 8 біт). Регістр-засувка використовується для роботи з мультиплексированной молодшої шиною адреси і даних. Для доступу до осередків пам'яті нам необхідно вказати 16-бітову адресу до 8-бітної осередку і тому ми використовуємо 8 КБ, то використовуватися будуть тільки 13 адресних ліній.

Автор застосував кварцовий резонатор 7.3728 МГц, щоб тимчасові характеристики інтерфейсу, при роботі з серією 74HC, були в нормі і уникнути включення додаткових програмних затримок.

Зовнішній вигляд модуля розширення

завантаження

Принципова схема і друкована плата модуля розширення (формат Eagle) - завантажити

В наступній частині ми розглянемо розподіл пам'яті і алгоритм роботи із зовнішньою пам'яттю, основні моменти при організації підпрограм читання / запису даних і протестуємо роботу зовнішнього модуля розширення пам'яті.

scienceprog.com